The idea of being able to simulate the ASICs from the information in this documentation was so obviously attractive that logic simulators were developed that could read the VHDL files. The standard MIL-STD-454N in Requirement 64 in section 4.5.1 "ASIC documentation in VHDL" explicitly requires documentation of "Microelectronic Devices" in VHDL. Department of Defense in order to document the behavior of the ASICs that supplier companies were including in equipment. In 1983, VHDL was originally developed at the behest of the U.S. 4.1 Synthesizable constructs and VHDL templates.The effort to standardize it as an IEEE standard began in the following year. The product of this effort was VHDL Version 7.2, released in 1985. In the early 1980s, the VHSIC Program sought a new HDL for use in the design of the integrated circuits it aimed to develop. VHDL is named after the United States Department of Defense program that created it, the Very High-Speed Integrated Circuits Program (VHSIC). To model analog and mixed-signal systems, an IEEE-standardized HDL based on VHDL called VHDL-AMS (officially IEEE 1076.1) has been developed. Since 1987, VHDL has been standardized by the Institute of Electrical and Electronics Engineers (IEEE) as IEEE Std 1076 the latest version (as of April 2020) of which is IEEE Std 1076-2019.

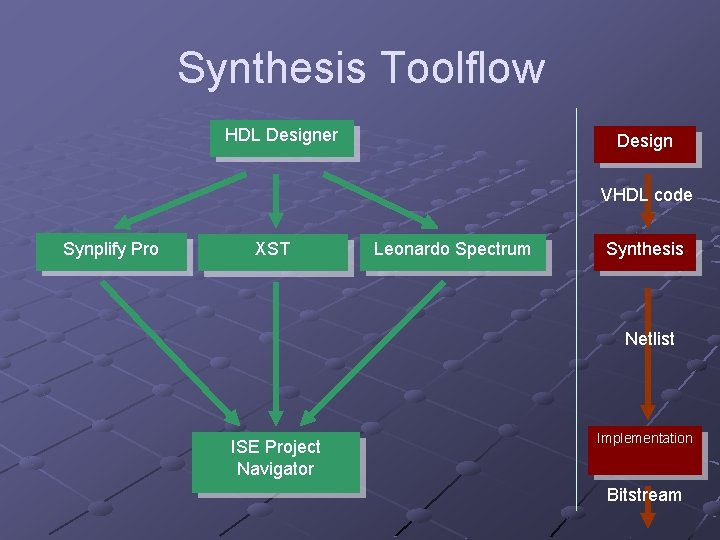

GENERATE HDL SCHEMATIC WITH SYNPLIFY PRO VERIFICATION

The VHSIC Hardware Description Language ( VHDL) is a hardware description language (HDL) that can model the behavior and structure of digital systems at multiple levels of abstraction, ranging from the system level down to that of logic gates, for design entry, documentation, and verification purposes.

0 kommentar(er)

0 kommentar(er)